Volume 4 Issue 11 November, 2016

# High Speed ADCs Employing Sigma Delta Modulation Technique: A Survey and Taxonomy

Mr.Premnarayan Shakya<sup>1</sup>; Mr.Deepak Sharma<sup>2</sup>

M.Tech Scholar<sup>1</sup>; Assistant Professor<sup>2</sup>

Lord Krishna College of Technology, Indore (India)<sup>1,2</sup>

shakyaprem78@gmail.com<sup>1</sup>; deepaksharma2189@rediffmail.com<sup>2</sup>

Abstract—In this paper, the performance of sigma delta modulators is measured and observed in the terms of signal to Noise ratio, for different Oversampling ratios for different order of Quantized bit. Also the sigma delta modulator is analyzed for different quantization level for the different parameters like Signal to noise distortion ratio, quantization noise rejection capability for medical devices. The result highlights the analysis of different order modulator, recording higher SNR of 82.5dB, which provides satisfactory results augmenting helps the device efficiency for different application.

Keywords— Sigma delta modulator, Signal to Noise Ratio, Dynamic Range, Quantization Noise

#### I. INTRODUCTION

In order to catch up with the present day technology advancements, sigma-delta converters are used with an aim of high level of reliability and functionality with reduced chip cost. It is applied in communication equipment, medical devices, automated production facilities, computers, weapons, navigation equipment, tools etc. Hence, if substantial analog signal processing (ASP) is performed, stochastic artifacts (noise) will accumulate, and the resulting signal may not represent the desired signal with the required significance.[1]

This paper focuses exclusively on delta-sigma modulation as chosen technique for A/D and D/A conversion. Based on the combination oversampling and quantization error shaping techniques Delta -sigma modulator achieve a high of insensitivity to analog imperfections, thus making them a appropriate choice to realize embedded analog-to-digital interfaces in modern systems-on-chip (SoCs) integrated in nanometer CMOS. Oversampling is inherently implemented in most sigma-delta (X-A) ADCs with integrated digital filters, where the modulator clock rate is typically 32 to 256 times the signal bandwidth, but X- A ADCs are limited for applications that require fast switching between input channels.

In medical applications multiple devices face the hurdle of SNR e.g. Electromyogram (EMG), Electrocardiogram (ECG), therefore the paper focuses on medical devices that require higher SNR to improve its performance.

High-performance data-acquisition signal chains used in medical equipment require wide dynamic range and high accuracy.

#### II. WORKING

#### A. Delta sigma modulation:

A delta-sigma converter uses many samples from the modulator to produce a stream of l-bit codes. The delta-sigma ADC accomplishes this task by using an input-signal quantizer running at a high sample rate. The delta-sigma modulator takes an input and produces a stream of digital values same as other quantizers that represents the voltage of the input. The delta-sigma modulators are of two types the time and the frequency domain.

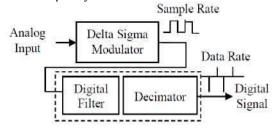

Figure 1: Basic first order delta sigma modulation

Sigma Delta Modulator contains a feedback loop, which is in the forward path of the loop. The modulator in Fig. l illustrates a first order sigma-delta modulator. It comprises of an integrator, a 1-bit quantizer, and a 1-bit DAC. The integrator ramps the input signals up and down. The integrator acts as the noise shaping circuit which shifts the noise from pass

Volume 4 Issue 11 November, 2016

#### Figure 2: Quantization process of Sigma Delta Modulator

### (2) QUANTIZATION AND QUANTIZATION ERROR

The discretization in amplitude domain of any continuous signal is known as quantization. The quantization enforces to discretize of amplitude of any continuous time signal.

This continuous-to-discrete transformation in amplitude generates an error, commonly referred to as quantization error. The quantization itself introduces a fundamental limitation on the performance of an ideal ADC. It degrades the quality of the input signal whose continuous-value levels are mapped onto a finite set of discrete levels.

Fig. 2(a) shows the transfer characteristic of an ideal quantizer, where e stands for the quantization error. This error is a nonlinear function of the input signal, as shown in Fig. 2(b). Note that, if x is confined to the full- scale input range [-XFS/2, XFS/2], the quantization error is bounded by [-A/2, A/2], with being the quantization step, defined as the separation between adjacent output levels in the quantizer.

#### (3) NOISE SHAPING:

The accuracy of Oversampling ADC / DAC can be increased by applying methods to reduce quantization noise. A method in which the in band noise is pushed in the frequency out of interest. Such a phenomena is called Noise Shaping ,where the quantization error conceptually generated by the difference of the input signal, , from an analog version of the quantizer output, -is shaped by a filter with a transfer function, usually called noise transfer function (NTF), which can be either of high-pass type or band-stop type. In case low pass oversampled signal, the low frequency in band component the removal of quantization[3].Noise can be done Differentiator in z domain transfer function is given by:

NTF

$$(z) = (1 - z^{-1}) L$$

(4)

Where L denotes the order of filter

$$DR = 20 * \log_{10} \left( \frac{2^Q}{1} \right) = 6.02 * Q \ dB$$

#### (4) DYNAMIC RANGE:

Dynamic range is the ratio of the smallest possible output (the least significant bit or quantum voltage) to the largest possible output (full-scale voltage).[6] It is measured as a ratio or as a base-10 or base-2 logarithmic value. Dynamic

band to stop band. The output of the integrator is given to the comparator and then the comparator output is fed back through a 1-bit DAC to the Summing circuit. Oversampling is the process of taking more samples per second than required on the basis of the Nyquist- Shannon criterion. By changing the sampling rate the signal power and total quantization noise power is not affected. Therefore, the signal to quantization noise ratio is not changed. However, the quantization noise is spread over a larger frequency range, which reduces the spectral density of the quantization noise. The quantization noise power is reduced by 3 dB for every doubling of the oversampling ratio and the signal to quantization noise ratio is improved accordingly if the original Nyquist band is considered only. The oversampling ratio also affects the signal to noise ratio. If oversampling is increased, the signal to noise ratio is also increased exponentially.

#### B. Parameters of delta sigma modulation:

#### (1) OVER SAMPLING RATIO:

When a significantly sampling frequency in a signal higher than the twice of bandwidth of digital samples known as Over sampling p, defined as

$$P = f_s / 2B \tag{1}$$

Where fs is the sampling frequency, B is the bandwidth or highest frequency of the signal, the nyquist rate is 2B.[2]

The theoretical limit of the SNR of an ADC measurement is based on the quantization noise due to the quantization error inherent in the analog-to-digital conversion process when there is no oversampling and averaging. Since the quantization error depends on the number of bits of resolution of the ADC the best case SNR is calculated as a function of the Effective Number of Bits

$$SNR = (6.02*ENOB) - 1.767$$

(2)

for the Effective number of bits , using the measured SNDR

$$ENOB = SNDR - 1.76 dB$$

Effective number of bits (ENOB) is simply the signal to noise-and-distortion ratio expressed in bits rather than decibels by solving the ideal SNR" equation [7] In the presentation of measured results, ENOB is identical to SNDR, with a change in the scaling of the vertical axis.

Volume 4 Issue 11 November, 2016 range is limited by quantization error. The maximum achievable dynamic range with N bit uniform the resolution of an ADC is increased, a point is the resolution of an ADC is increased, a point is

range is infinited by quantization error. The maximum achievable dynamic range with N bit uniform quantization is defined as the largest rms value of sine-wave to rms noise as shown in equation (5). Oversampling allows an ADC to achieve high dynamic range at low cost, while also addressing tough space, thermal, and power design challenges.

#### (5) FIGURE-OF-MERIT:

Comparison of the power efficiency of two AD converters that achieve identical signal conversion specifications, i.e. have the same sampling rate and realize the same SNR for every input signal, is an easy task; the one with the lowest power consumption is the best. However, if the signal conversion specifications are not 100% identical, the comparison becomes difficult. To overcome this problem and make the comparison of different data converters possible, typically a Figure-of-Merit (FoM) is calculated. In the FoM a single value is used to represent the performance specifications of the converter, typically the power consumption and the signal conversion bandwidth and resolution. Unfortunately, no universally agreed standard exists for calculation of the FoM. An often used FoM equation for the characterization of AD converters equals

$$FoM = \frac{P}{2^{ENOB}.\min(f_{5}, 2.ERBW)}$$

(6)

In this equation P equals power, ENOB equals the number of effective bits measured for a DC input signal, Fs equals the sampling rate, and ERBW is the effective resolution bandwidth. The ENOB is calculated as

$$ENOB = \frac{SINAD - 1.76}{6.02} \tag{7}$$

where the SINAD is measured for a (near) DC input.

The ENOB of the 5th order modulator is found to be 13.4. The effective resolution bandwidth is equal to the frequency that results in a 3 dB SINAD reduction compared to the SINAD at DC. The unit of the FoM of Eq. 6 is Joules per conversion step. As a result, a lower value is better. Sometimes the inverse of Eq. (6) is used such that a higher FoM number represents a better result.

Although the FoM of Eq. (6) is widely used, it cannot be used to make fair comparisons between low

resolution and high resolution AD converters. When the resolution of an ADC is increased, a point is reached where thermal noise is limiting the SNR. In order to reduce the impact of the noise by 3 dB, capacitances need to be doubled. To increase the number of effective bits by one, a 6 dB reduction of the noise is required, which means a factor four increase in capacitance. Since power scales linearly with the amount of capacitance to charge, the power will also increase with a factor four. Thus, the FoM will become at least a factor 2 worse when the ENOB is increased by one.

In conclusion, for comparing DAC performance sometimes the FoM of Eq. 5 is used, but no actual de factor standard exists. However, the part of the power consumption is, by definition, required to drive the load, straightforward application of Eq. 5 can lead to incorrect conclusions. Other FoM measures used for DAC Characterization include SNR.

#### III. REALIZATION

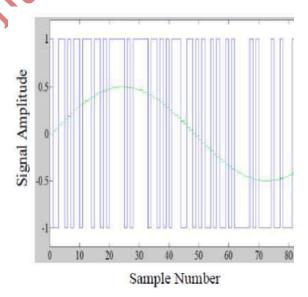

First order Sigma Delta Modulator is realized using MATLAB, by providing the input parameters as OSR = 32, Quantization Level = 8. Figure 3 shows the magnitude response of the NTF.

Figure 3 Magnitude response of Delta sigma modulator

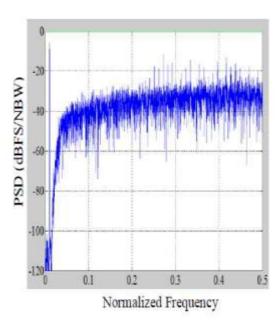

Fifth order Sigma Delta Modulator is realized using MATLAB by providing the input parameters as OSR= 32, Quantization Level = 8. Figure 4 shows the SNR= 82.5dB of the time domain analysis of sigma delta modulator.

Volume 4 Issue 11 November, 2016

Figure 4 Analysis of SNR of delta sigma modulation

The quality factor is measured of sensitivity of pole location to perturbation. Quality factor value of each system is found by observing phase and magnitude of each pole and choosing the largest value from all possible values of quality factor. The dynamic range and quality factor of the 5th order modulator is found 48.17 dB and 7.0657 respectively.

Table 1: The comparison values of SNR for Quantization level = 8

| S.NO | OSR | SNR(dB) |

|------|-----|---------|

| 1.   | 2   | 20.5    |

| 2.   | 3   | 21.3    |

| 3.   | 4   | 23.4    |

| 4.   | 8   | 30.3    |

| 5.   | 16  | 36.3    |

| 6.   | 32  | 42.7    |

| 7.   | 64  | 28.8    |

| 8.   | 128 | -18.7   |

Table 1 shows the comparison of SNR and Oversampling ratio. The SNR value is directly proportional to Oversampling ratio to a certain value. After a maximum certain point SNR starts decreasing although the OSR value is increased and to be found out negative in dB.

Signal Input Level (dB)

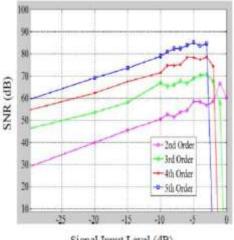

Figure 5 shows the comparison of SNR vs signal input level for different order. SNR ratio also depends on signal input level. As the signal input level increases SNR increases to a maximum value. After a maximum level the SNR value drops towards  $0 \, dB$ .

#### IV. CONCLUSION

In this paper the various parameters is shown which affects the SNR ratio. In Medical application devices requires high SNR ratio for their higher performance. If the order of quantizer bit is increased, the peak SNR value can be achieved at lower OSR at certain limit, after that OSR will not affect the SNR value, after reaching a specific level of quantization with the increase in OSR, the SNR suddenly increases, with increase in effective number of bits and increase in Quantization noise reduction. It is found the higher SNR value of 82.5 dB for fifth order modulator.

#### **REFRENCES**

- Norsworthy . S, Schreier . R and Temes.G, [1] —Delta (Editor), Sigma Convereters||,IEEE Press ,Wiley Interscience Publication, United States of America, 1997.

- "Sigma-Delta [2] Jose M. de la Rosa., Modulators: Tutorial Overview, Design Guide, and State-of- the-Art Survey", IEEE Transactions on circuits and systems—I: regular papers, vol. 58, No. 1, Jan. 2011.

- Sangil Park., "Principles of Sigma-Delta [3] Modulation for Analog-to-Digital Converters", APR8/D Rev1. Motorola.

- [4] Joshua D. Reiss., "Understanding Sigma-Delta

## IJournals: International Journal of Software & Hardware Research in Engineering ISSN-2347-4890

Volume 4 Issue 11 November, 2016

Modulation: The Solved and Unsolved Issues". J. Audio Eng. Soc., Vol. 56, No. 1/2, January/February 2008

- [5] J. Silva, U. Moon, J. Steensgaard And G.C. Temes —Wideband Low-distortion Delta-Sigma ADC Topology|, Electronics Letters, IEEE Conference, Vol. 37, Issue: 12, pp 737-738, Jun 2001.

- [6] Benoit Dufort And Gordon W. Roberts, Signal Generation Using Periodic Single And Multi-bit Sigma- Delta Modulated Streams!, International Test Conference, IEEE Conference, pp 396-405, November 1997

- [7] Walter Kester. Measure ash-ADC performance for trouble-free operation. EDN, pages 103-114, February 1, 1990.

- [8] Robert H. Walden. Analog-to-digital converter survey and analysis. IEEE Journal on Selected Areas in Communication, 17(4):539-550, April 1999.